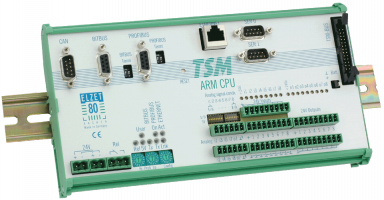

TSM - ARM-CPU

Ethernet joins traditional IT and control engineering: on one hand the built-in web server opens control tasks to the office world, on the other hand I/O functions can directly be called on the TSM-ARMCPU.

The board was developed in order to meet the demand for direct integration into the Ethernet. We selected the S3C4530 processor because besides its ARM-core and Ethernet interface it has a HDLC-controller that is used by the BITBUS-fieldbus. This way subnets can be built very cost effectively: Ethernet for communication with the production planning layer and BITBUS for the field if necessery over long distances which would be very expensive to achieve with Ethernet alone.

- 32bit processor S3C4530 with ARM7TDMI core, cache, DMA, HDLC (Bitbus), 2 32bit timers, 2 ser. interfaces with Rx and Tx FIFOs, I²C and Ethernet controller 10/100MBit

- 4MByte flash-EPROM, 2 MByte RAM with 32bit-data-bus

- 512K flash (sectored) allowing updates of operating system

- mCAT2 realtime core with “Express-I/O” for convenient I/O access

- RAM battery backed-up

- realtime clock with calendar

- 2 independent RS232 interfaces

- 1 isolated RS485 network interface (BITBUS)

- Relays (change over switch) 1A/30V

- configuration switch 0..F

- optional: CAN interface or Profibus slave interconnection

Process I/O:

- 8 digital inputs 24V, optoisolated; optional as counters

- 8 digital outputs 24V, 1,5A, optoisolated and overload protected; programmable as PWM-output

- 8 analog inputs 10 Bit; 0..5V, 0..20mA or KTY

- 2 analog outputs 8 bit; 0..5V

- Prices

- Webserver

- Hardware

- Process-I/O

- Programming

- Installation

Prices

prices on request

TSM-ARMCPUEA

Module with 32bit memory: 4MB flash-EPROM and 2MB RAM, with Ethernet and BITBUS, with I/O (8E/8A, 8E/2A analog), without CAN, without Profibus

Please order battery and connector terminals separately:

TSM-ARMCPU<XSK

prices on request

Connector set: spring force terminal blocks with 381mm contact spacing for the I/O, 5,08mm screw terminal blocks 24V-supply and relay

* all prices ex works (+VAT/MwSt inside Germany)

Webserver

mCAT2 offers a TCP/IP stack on the TSM-ARMCPU for the Ethernet that has been developed regarding the demands of a realtime operating system. Up to 3 parallel HTTP servers are possible: one will serve at the standart port, port 80, (e.g. for a webpage with datasheet of the board and configuration settings), the other ones can be used at the customers descretion.

Static contents (PDF-data-sheets, GIF-images etc.) needed for webpage design can be stored in the flash. A little tool will pack a prepared subdirectory on your Windows® computer into a downloadable file for the flash-EPROM and sets the MIME-type.

The compression ist optimized so that the decompression will need little computing time and will not be a large load on the TSM-ARMCPU..

An mCAT task can register a CGI-function at at the HTTP-server and will get the corresponding HTTP queries. A function for splitting the received HTTP-GET data is available and a function similar to vprintf() for creating the HTML-answer-page.

To conveniently access i/o on the ARMCPU from a Windows® client, a nodeAccess™-DLL will call the nodeAccess server on the ARMCPU to have access to all Express-i/o inputs, outputs and user defined SOFTBUS variables.

Hardware

The RAM can be backed-up optionally by a large lithium cell which is clipped to the case and which also supplies the highly accurate I²C-realtime-clock. The battery is able to ensure long backup time and can be exchanged when the module is operating. There is also a serial EEPROM at the I²C-bus with 64 words for storing configuration data like network address, serial interface speed etc . Besides to that, there is a rotary switch labeled "config" with 16 positions that can be set by the user for example to choose a special application or operating mode.

The isolated Ethernet interface is accessible at a RJ45 connector and automatically detects 10 or 100 MBit. Domain-name-server address, MAC and IP address etc. are stored in the EEPROM. TSM-ARMCPU has two standard UART interfaces, those are RS232-driven and are accessible through two 9pin D-connectors. RTS and CTS are supported as handshake signals, DTR is acitvated when the CPU is turned on. The built-in HDLC-interface enables the TSM-ARMCPU as BITBUS slave or master. The interface is implemented as RS485 half-duplex-interface accordingly, but can also be switched to full-duplex or RS422 point-to-point with DIP-switches. A termination, as it is required at the physical end of the cable, can also be turned on with the DIP-switches.

mCAT allows due to its included Bitbus support direct access from the master (e.g. PC) to all modules up to the last TSM-module. A large part of the Express-I/O-functions can be directly used over the BITBUS, when using ELZET80's OPC-Server for BITBUS even from all PCs connected to the same network as the master. TSM-ARMCPU is also ideal for the "distributed control"-concept which is favored by the BITBUS: Each mCAT-task can also be a BITBUS-task - including dynamic downloading, activation and deleting. After all TSM-ARMCPU can also work as gateway between Ethernet and BITBUS.

If BITBUS is not needed, one of the RS232-interfaces can alternatively work as asynchronous, isolated RS485-interface over the half-duplex-driver of the BITBUS.

An isolated output with max. 1A at 30V can be used for example as "controller ready"-signal. In combination with the watchdog circuit, which initiates reset on voltage interruption or missing retriggers by the software (has to be initialized), an effective emergency-stop-circuit can be implemented.

Process-I/O

Eight inputs and eight outputs, both 24 V, in addition to eight analog inputs and two analog outputs are available for the actual control task. Three pin terminals are available for each input, to enable a simple connection of supply, signal and ground, for example for ordinary (PNP) proximity switches. The inputs have an ESD, burst and surge resistant protection setup with low pass filter and optoisolators and show the input condition with red LEDs. Threshold values and currents are subject to the standards.

The inputs can be used as counters: either all eight as frequency counters or four as frequency counters and one as event counter or two as event counters.

The eight outputs are p-switching (high-side), that means they supply a grounded load, what guarantees safety of accidental grounds in the cable. The outputs drive 0,7A each through the complete temperature range up to 70°C, but due to the connectors circuits not more than 8A altogether can be drawn.

Not only voltages between 0 and 5V can be applied to the analog inputs, with two DIP-switches at each input they may be used for 0..20mA process current or directly Si-temperatur-sensors (2kOhm) like KTY10 or KTY82. For the analog inputs there is a separate power supply branch with reference and sensor voltage from a linearly controlled 12V-intervoltage.

TSM-ARMCPU is optionally avialable with CAN-interface at a 9pin D-connector. For further information regarding software support please contact us.

Also optionally available is a Profibus-Slave-interconnection. Two rotary switches are used to enter the slave address. Profibus is supported by mCAT.

At the TSM-bus-connector up to 16 i/o-modules with a total power consumption of 3,5A can be connected.

Programming

The ARM-CPU is programmed in C based on the ported mCAT2-realtime-core that we are already using with our TLCS900 products. mCAT offers time or event based communication via messages between different tasks or between interrupt drivers and tasks. The hardware abstraction layer,“Express-I/O”, enables access to I/O with assigned names to any analog and digital inputs and outputs. IN(&boilertemp) or OUT(&motor) for example let you handle logical units, they can also be assigned to other physical I/O if necessary. The serial interfaces are supported by convenient interrupt drivers that can be parameterized with several filter functions and with start and end sequence inspection. Data storage in the failsafe RAM works with assistance of the BgMEM-memory for FIFO, LIFO or circular memory structures.

For TSM-ARMCPU there is a very good C compiler from Metaware but it is quite expansive. There is also a good open source alternative called GNUDE which includes the gnu-C compiler and runs on Windows. On the mCAT developer disc we have included GNUDE prepared for your projects.

Software conversion when switching from TSM-CPUxxH2 can be reduced to adaptation of that part of I/O access that is not done with Express-I/O, e.g. to processor integrated peripherals and orientation of variables to 4Byte limits that are necessary on the ARM processor.

The operating system mCAT is - just as applications later on - to be downloaded to the CPU via "Bootmon" (in 8bit flash) into the programm flash (1Mx32) on the ARMCPU - this way mCAT and user tasks benfit from the fast 32bit access. All programming and also deleting of pages (blocks) in the flash-EPROM is done with monitor commands via the BITBUS. mCAT supports optional programming into the RAM (if memory is battery backed-backed up even auto starting) for testing or into the flash-EPROM.